LiDAR-Based Obstacle Avoidance

Published:

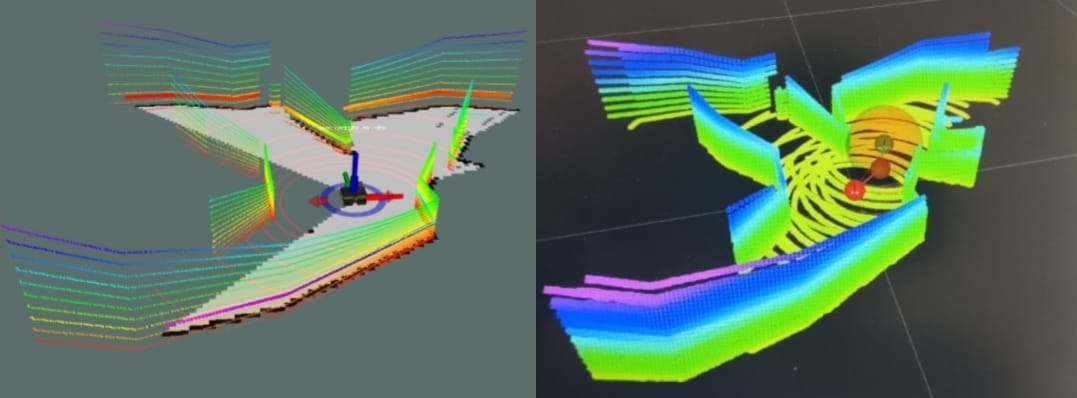

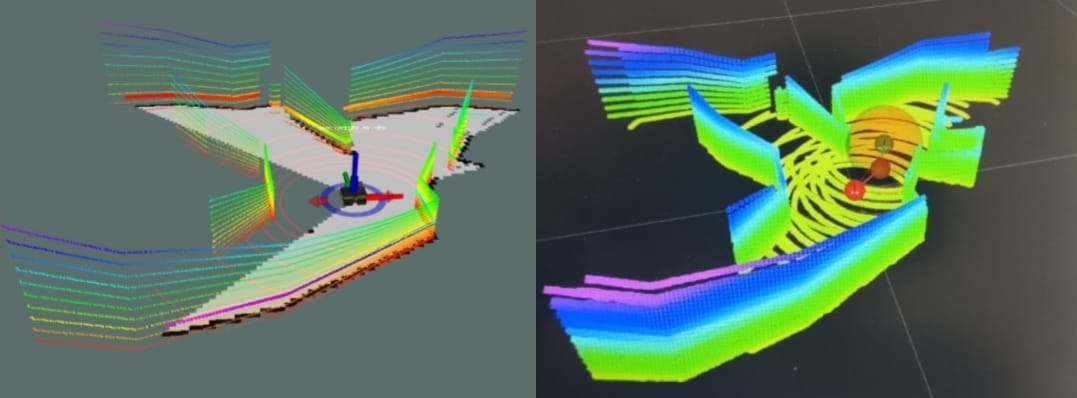

Developed LiDAR-based navigation for warehouse robotics.

Published:

Developed LiDAR-based navigation for warehouse robotics.

Published:

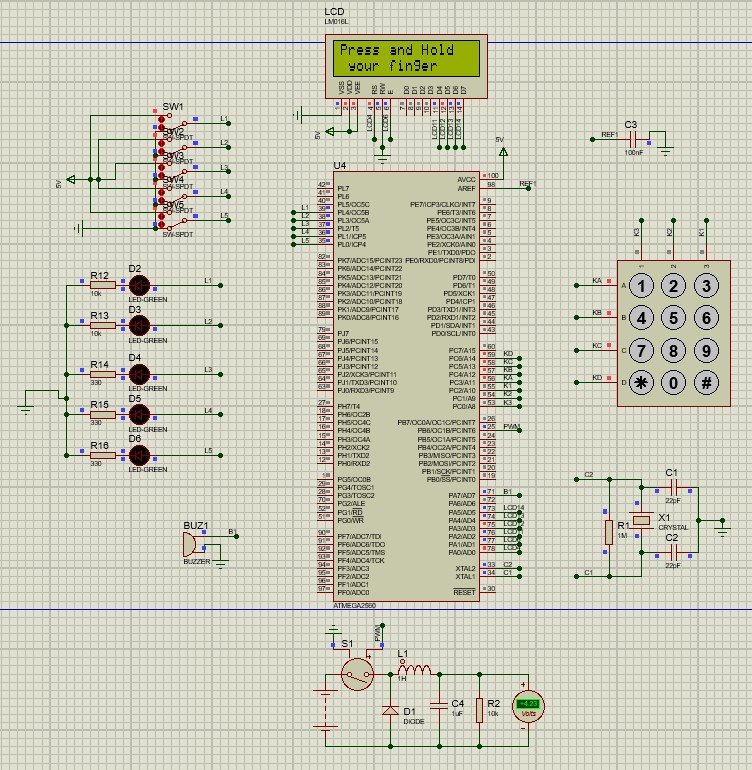

Designed an electronic voting machine using Proteus software that utilizes voter verification. This project aimed to address the issue of voter fraud and ensure that only eligible voters are able to cast their ballots.

Published:

Created robotic arm for automated vehicle charging.

Published:

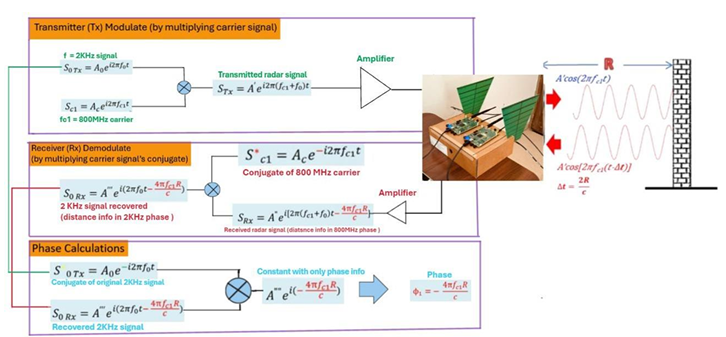

Developed tools for analyzing wireless channels and Doppler effects.

Published:

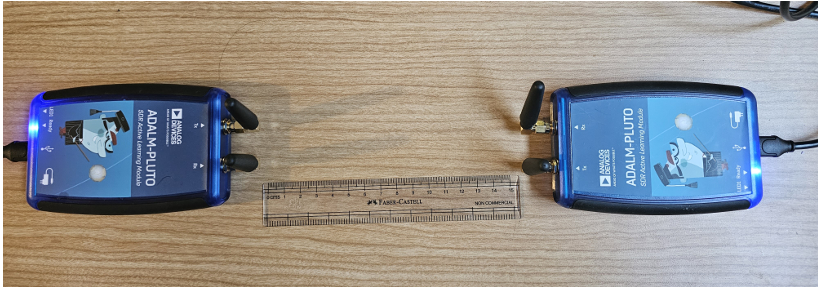

Operated Ettus USRP B210 SDR for object distance measurement and radar system design.

Published:

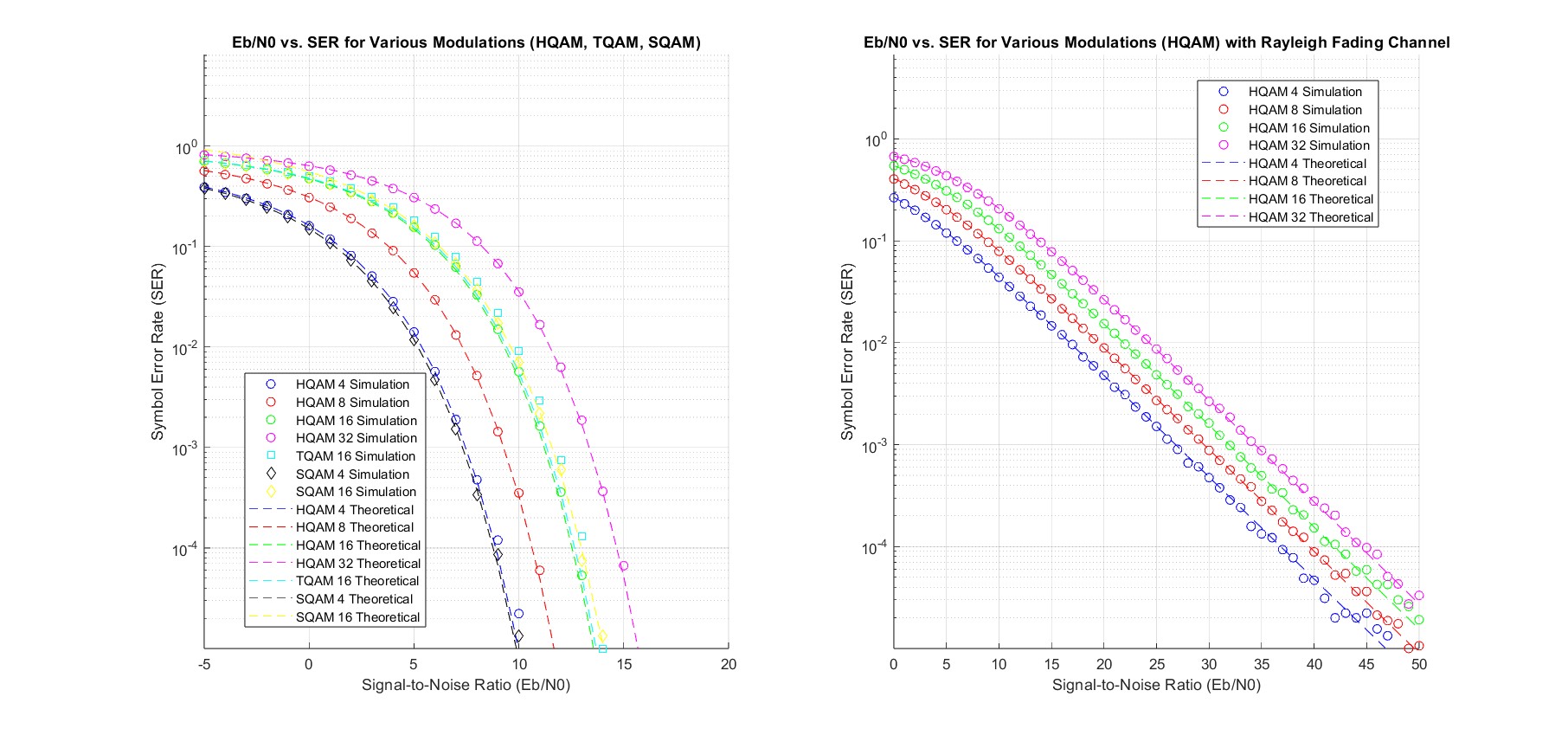

Accurate ASER estimation for HQAM under AWGN and Rayleigh fading conditions.

Published:

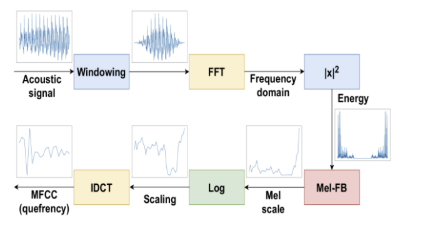

Designed a fixed-point DSP hardware accelerator for MFCC extraction, implementing pre-emphasis, framing/windowing, 512-point FFT, Mel filterbanks, log scaling, DCT, and liftering in Verilog. Achieved <1% numerical error vs. MATLAB reference with ∼7.7µs latency per frame, enabling real-time speech processing for low-power IoT devices.